Consulte las especificaciones para obtener detalles del producto.

Encyclopedia Entry: 74LVT16373ADGG,512

Product Overview

Category

The 74LVT16373ADGG,512 belongs to the category of integrated circuits (ICs) and specifically falls under the family of LVT (Low Voltage Transceiver) series.

Use

This IC is primarily used as a high-speed, low-voltage octal transparent latch with 3-state outputs. It is commonly employed in digital systems for data storage and transfer applications.

Characteristics

- High-speed operation: The 74LVT16373ADGG,512 offers fast latch and output switching times, making it suitable for time-critical operations.

- Low voltage operation: It operates at a low voltage range, typically between 2.7V and 3.6V, which makes it compatible with modern low-power electronic devices.

- 3-state outputs: The IC features 3-state outputs, allowing multiple devices to share a common bus without interference.

- Robust design: It has built-in protection against electrostatic discharge (ESD), ensuring reliability in various environments.

Package and Quantity

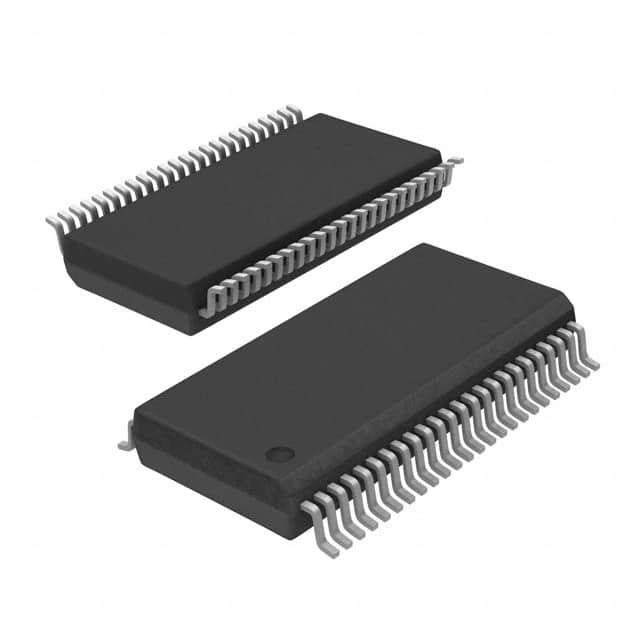

The 74LVT16373ADGG,512 is available in a surface-mount TSSOP (Thin Shrink Small Outline Package) package. Each package contains one IC.

Specifications

- Logic Family: LVT

- Number of Bits: 8 (octal)

- Input/Output Type: 3-state

- Supply Voltage Range: 2.7V - 3.6V

- Operating Temperature Range: -40°C to +85°C

- Package Type: TSSOP

- Manufacturer Part Number: 74LVT16373ADGG,512

Pin Configuration

The IC has a total of 48 pins, arranged in a dual in-line package (DIP) format. The pin configuration is as follows:

Pin 1: GND

Pin 2: D0

Pin 3: D1

Pin 4: D2

Pin 5: D3

Pin 6: D4

Pin 7: D5

Pin 8: D6

Pin 9: D7

Pin 10: OE#

Pin 11: LE#

Pin 12: CP

Pin 13: A0

Pin 14: A1

Pin 15: A2

Pin 16: A3

Pin 17: A4

Pin 18: A5

Pin 19: A6

Pin 20: A7

Pin 21: VCC

Pin 22: Q0

Pin 23: Q1

Pin 24: Q2

Pin 25: Q3

Pin 26: Q4

Pin 27: Q5

Pin 28: Q6

Pin 29: Q7

Pin 30: GND

Pin 31: Q7#

Pin 32: Q6#

Pin 33: Q5#

Pin 34: Q4#

Pin 35: Q3#

Pin 36: Q2#

Pin 37: Q1#

Pin 38: Q0#

Pin 39: GND

Pin 40: D7#

Pin 41: D6#

Pin 42: D5#

Pin 43: D4#

Pin 44: D3#

Pin 45: D2#

Pin 46: D1#

Pin 47: D0#

Pin 48: VCC

Functional Features

The 74LVT16373ADGG,512 offers the following functional features: - Transparent latch: The IC allows data to pass through when the latch enable (LE#) input is high. - 3-state outputs: The outputs can be put in a high-impedance state by asserting the output enable (OE#) signal, allowing multiple devices to share a common bus. - Edge-triggered clocking: The IC utilizes a clock pulse (CP) input to latch the data on the rising edge of the clock signal.

Advantages and Disadvantages

Advantages: - High-speed operation enables efficient data transfer. - Low voltage operation reduces power consumption. - 3-state outputs facilitate bus sharing in complex systems. - Robust design protects against electrostatic discharge.

Disadvantages: - Limited number of bits (8) may not be suitable for applications requiring larger data storage.

Working Principles

The 74LVT16373ADGG,512 operates based on the principle of transparent latching. When the latch enable (LE#) input is high, the data inputs (D0-D7) are passed through to the corresponding outputs (Q0-Q7). The latch "transparent" state allows real-time data propagation. The clock pulse (CP) input triggers the latch to capture the

Enumere 10 preguntas y respuestas comunes relacionadas con la aplicación de 74LVT16373ADGG,512 en soluciones técnicas

Question: What is the function of the 74LVT16373ADGG,512 in a technical solution?

Answer: The 74LVT16373ADGG,512 is an octal transparent latch with 3-state outputs. It is used to store and control the flow of data in digital circuits.Question: What is the maximum operating voltage for the 74LVT16373ADGG,512?

Answer: The maximum operating voltage for this device is typically 3.6V.Question: How many latch outputs does the 74LVT16373ADGG,512 have?

Answer: This device has 8 latch outputs, allowing it to store and control 8 bits of data.Question: Can the 74LVT16373ADGG,512 be used in high-speed applications?

Answer: Yes, the 74LVT16373ADGG,512 is designed for high-speed operation and can be used in applications where fast data transfer is required.Question: Does the 74LVT16373ADGG,512 support 3-state outputs?

Answer: Yes, this device has 3-state outputs, which means that the outputs can be disabled or put into a high-impedance state when not in use.Question: What is the power supply voltage range for the 74LVT16373ADGG,512?

Answer: The power supply voltage range for this device is typically between 2.7V and 3.6V.Question: Can the 74LVT16373ADGG,512 be cascaded to increase the number of latch outputs?

Answer: Yes, multiple 74LVT16373ADGG,512 devices can be cascaded together to increase the number of latch outputs in a system.Question: What is the maximum operating frequency for the 74LVT16373ADGG,512?

Answer: The maximum operating frequency for this device is typically around 200 MHz.Question: Does the 74LVT16373ADGG,512 have any built-in protection features?

Answer: Yes, this device has built-in protection against electrostatic discharge (ESD) and excessive power dissipation.Question: Can the 74LVT16373ADGG,512 be used in both parallel and serial data transfer applications?

Answer: Yes, this device can be used in both parallel and serial data transfer applications, depending on the specific requirements of the system.